# Design and Analysis of a Low-Voltage Double-Tail Comparator for Flash ADC at 180nm and 90nm CMOS Technology

Anu, RM Singh

**Abstract**— Low power double tail dynamic comparator architecture is presented in this paper that performs better in low supply voltage applications. The main idea of this design of CMOS comparator is to increase the latch regeneration speed by increasing the intermediate voltages. For this purpose, two control transistors in a cross-coupled manner are added to the first stage in parallel to input transistors. The results were simulated in Cadence Virtuoso Analog Design Environment with GPDK 90nm technology and 180nm technology. The proposed structure shows significantly lower power dissipation, higher speed compared to the dynamic comparators present in the literature. The average power of proposed comparator in 90nm technology is 83.92% reduced than at 180nm technology due to the decrease in channel length of the transistors and it is 62.78% reduced as compared to the double tail dynamic comparator. The delay of proposed comparator is 28% reduced when compared to the double tail dynamic comparator in 90nm technology. Thus, the proposed transistor is energy efficient when compared to other topologies at 90nm and 180nm technologies.

Index Terms— Clocked regenerative comparators, Convention dynamic comparator, Double tail dynamic comparator, Flash ADC, Multithreshold logic, Pre-amplifier based comparator, Regenerative comparators.

#### **1** INTRODUCTION

The electronics industry has the vast demand for portable battery operated devices with decreasing technology over

the last few years where the low power methodologies are main concern for high speed applications. CMOS technology is continuously growing with minimum feature sizes which are the largest segment of the total worldwide sales [1]. The transistor size is being scaled to smaller dimensions that results in higher performance with lesser chip size due to which MOS transistors are occupying the large part of industry [2]. With increasing the scaling of transistors, more transistors, faster and smaller, could be packed into a chip that increases to the operating frequency and processing capacity per chip [3]. The process variations and other non-idealities such as speed, stability, leakage power, noise of the circuit has significant influence the overall performance of the device when moving towards smaller feature size processes [4]. There are many applications where low power dissipation [19], low noise, high speed [20], less offset voltage [22] and higher performance [30] is required for Analog to Digital Converters for mobile and portable devices [5][6]. Comparators and interstage gain amplifiers are the performance limiting blocks in such ADCs. A comparator compares an analog input voltage with another anolog input signal or a reference signal and then it gives a logic output according to the input voltage difference. The accuracy and speed of comparators, along with power consumption, are the keen topics for achieving overall higher performance of ADCs [15] [31]. For fast operation of the comparator, it must quickly pass through the transition region of the analog signal. The designing of low power CMOS Comparator is one of the challenges faced when the supply voltage and transistor channel lengths are scaled down with each generation of CMOS technologies. There exists a tradeoff among power, speed, stability and various other performance parameters at different aspect ratios. The designing of a CMOS Comparator with a combination of less propagation delay and

low power is quite challenging. There are various circuit topologies and their implementation techniques to evade this problem.

Clocked regenerative comparators are based on latch stage that forces a fast decision due to positive feedback i.e. crosscoupled inverters which are fundamental circuit blocks mainly used in Flash ADCs due to their high speed decision speed [4] [7]. Sometimes an additional block is added to comparators like a preamplifier stage that intensifies the resolution [3]–[5] or an offset compensation circuitry could also be added for increasing the performance of the comparator [6]. In the past, pre-amplifier based comparators were used for Flash and Pipelined ADC architectures [6] – [10]. The main drawbacks of pre-amplifier based comparators were the less speed and more offset voltage [11]. There are various applications of comparators other than Flash ADCs [14]. A current-mode latch comparator was implemented in 40-GBit/s demultiplexer at 0.11µm CMOS technology at a supply voltage of 1.2V with a bandwidth modulation technique that extracted every fourth bit of a 40-GBit/s data stream [7]. In [8], Leakage power was reduced for optimization of comparator that used Multithreshold (MCTMOS) logic, and Reversible gates and one to one mapping is used in paper [9]. A rail-to-rail folded-cascode amplifier [10] with a positive feedback connection of two backto-back inverters that used only reset switches for controlling with input voltage range of 1.6 V with 1mV accuracy and total power consumption of the comparator is  $300\mu$ W with biasing current of 11µA and offset voltage of 1mV [10]. DC gain method was described in [11], which used a high DC-gain rail-torail folded-cascode amplifier for high speed applications by using switches of two types i.e. reset and latch for increasing the speed of the comparator's comparison process, whereas a trimmable latch comparator was described in [12].

There are various topologies of comparators like rail to rail comparator [13], capacitive dynamic comparator [16], leakage

tolerant comparator [17], improved single stage kickback rejected comparator [18], parallel prefix tree comparator [21], binary comparator [22] [28], reversible quantum comparator [29], charge sharing dynamic latch comparator [35], and switched current comparator [36]. In general, dynamic comparators could be used for high speed operations for Flash and Pipelined ADCs that used clock for the comparison process. However, dynamic comparators have large switching power dissipation as compared to pre-amplifier based comparators which are used in flash ADCs, null detectors, window detectors, zero-crossing detectors, relaxation oscillator, level shifter, site and remote sensing systems, microcontrollers, digital imaging systems, etc.

This paper presents conventional dynamic comparator in section I, section II contains dual tail comparator and section III discusses the proposed comparator. The simulated results of comparators at 180nm and 90nm technology nodes are comprised in this paper with their performance parameters such as voltage supply, propagation delay, power dissipation, and energy consumption in section IV. The conclusions and future scope of comparator designs are discussed in section V of this paper.

### **2 CONVENTIONAL DYNAMIC COMPARATOR**

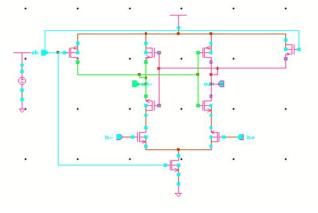

Conventional dynamic comparator has rail-to-rail output swing with high input impedance, and less static power consumption. The schematic diagram of the comparator is shown in Fig 1. In conventional dynamic comparator, during the reset phase when clock is zero and tail transistor is off, a valid logical level is achieved during reset as reset transistors pull both output nodes ( $Out_n \& Out_p$ ) to supply voltage. During comparison phase, when clock is equal to supply voltage, tail transistor is on. Depending on the corresponding input voltage, output voltages which were pre-charged to supply voltage starts to discharge with different discharging rates.

Let  $V_{IN+} > V_{IN-}$ , so  $Out_p$  gets discharged faster than  $Out_n$  i.e.  $Out_p$  to fall down to  $V_{DD}$ – | Vthp | before  $Out_n$ , the latch regeneration gets initiated by back-to-back inverters when corresponding PMOS transistor will turn on. Thus,  $Out_n$  gets charged to  $V_{DD}$  while  $Out_p$  drops to ground. The circuits works vice versa when  $V_{IN+} < V_{IN-}$ .

Fig1. Schematic of Conventional Dynamic Comparator

## **3 DOUBLE TAIL DYNAMIC COMPARATOR**

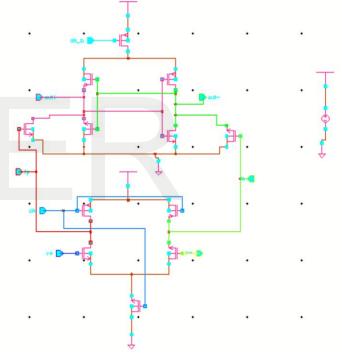

Double Tail Dynamic Comparator has less stacking of transistors and thus it can be operated at lower supply voltages as compared to the conventional dynamic comparator. For fast latching independent of the input common-mode voltage (V<sub>cm</sub>), double tail enables a large current in the latching stage with wider tail transistor, and double tail also provides a small current in the input stage for lower offset. During reset phase of comparator when clock is zero, the tail transistors are off. The intermediate nodes are charged to supply voltage. During decision-making phase when clock is equal to supply voltage, the tail transistors are on, so voltages at intermediate nodes start to drop with the rate defined by tail current and the capacitance of input transistor. The intermediate stage passes the voltage difference to the cross-coupled inverters. This stage also provides reduced kickback noise i.e. good shielding between input and output. The schematic of double tail dynamic comparator is shown in Fig 2.

Fig2 Schematic of Double Tail Dynamic Comparator

### **4 PROPOSED COMPARATOR**

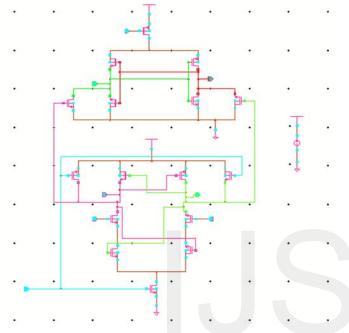

The proposed comparator is designed which is based on the double-tail topology as its performance is better in low supply voltage applications. The intermediate voltages are increased so that the latch regeneration speed gets increased by adding two control transistors to the first stage of proposed comparator in parallel to input transistors but in a cross-coupled manner as shown in schematic. During reset phase of comparator, clock is zero and the tail transistors are off, thus avoiding static power consumption, the intermediate nodes are charged to the supply voltage. During decision-making phase when clock is equal to supply voltage then the tail transistors are on. Furthermore, the control transistors are in off stage at the begin-

IJSER © 2015 http://www.ijser.org ning of this phase. Thus, the intermediate node voltages begin to drop in accordance of input supply with different rates. Let  $V_{IN+} > V_{IN-}$ , thus positive intermediate node voltage drops faster than other one, since positive node discharge faster than the negative node. The corresponding PMOS control transistor starts to turn on as long as negative node continues falling that pulls positive node back to the magnitude of voltage supply, thus other control transistor remains off during this period that allows negative intermediate node to be discharged completely. The proposed comparator is shown in Fig 3.

Fig3. Schematic of Double Tail Dynamic Latch Comparator

### **5 SIMULATION AND RESULTS**

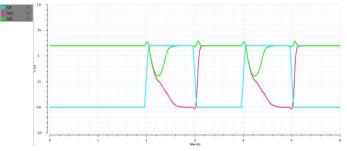

The Comparators are analyzed in Cadence Virtuoso Environment with a supply voltage of 600mV. Conventional dynamic comparator schematic is shown in Fig 1. The circuit is simulated with its input voltage as 300mV and reference voltage as 295mV. The clock of the dynamic comparator has amplitude of 600mV with rise and fall time of 0.08ns for a period of 1ns. The circuit is examined under transient analysis for duration of 6ns output waveforms is shown in Fig 4. The average power of conventional dynamic comparator is 12.69 $\mu$ W, propagation delay of 1.93ns with settling time as 5.964 ns and the speed of operation of comparator is 518.13 MHz.

Fig4. Simulations of Conventional Dynamic Comparator

The Double Tail Dynamic Comparator is analyzed in Cadence Virtuoso Environment with a supply voltage of 600mV whose schematic is shown in Fig 2. The circuit is simulated with its input voltage as 300mV and reference voltage as 295mV. The clock of the dynamic comparator has amplitude of 600mV with rise and fall time of 0.08ns for a period of 1ns. The circuit is examined under transient analysis for duration of 6ns output waveforms is shown in Fig 5. Average Power of double tail dynamic comparator is 7.85 $\mu$ W, with propagation delay of 361.2ps, whereas PDP of comparator is 2.835fJ with a settling time of 5.988 ns, and energy of 0.0471pJ.

Fig5 Simulations of Double Tail Dynamic Comparator

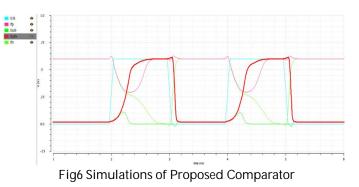

The Proposed Comparator was designed in Cadence Virtuoso Environment with a supply voltage of 600mV whose schematic is shown in Fig 3. The circuit is simulated with its input voltage as 300mV and reference voltage as 295mV. The clock of the proposed comparator has amplitude of 600mV with rise and fall time of 0.08ns for a period of 1ns. The circuit is examined under transient analysis for duration of 6ns output waveforms is shown in Fig 6. The average power of the proposed comparator is 2.921µW with a delay of 259.7 ps so the PDP comes out to be equal to 0.7585fJ. The settling time of the waveform is 5.978 ns. The speed of operation of the comparator is 3.850 GHz.

The Power waveform of Proposed Comparator is shown in Fig 7 during a charging and pre-charging phase for a period of 6ns.

Fig7 Power Dissipation for duration of 6ns

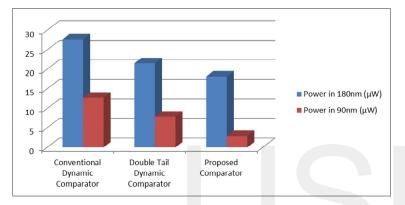

The power consumption of conventional dynamic comparator, double tail comparator and proposed comparator is shown in Fig 8 at 180nm and 90nm technologies.

Fig8 Power of Comparator Topologies at 180nm and 90nm

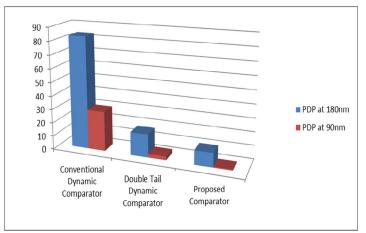

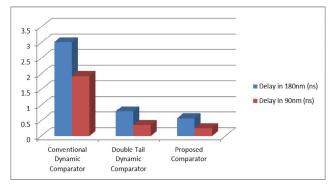

The propagation delay and PDP of conventional dynamic comparator, double tail dynamic comparator and proposed comparator at 180nm and 90nm technologies is shown in Fig 9 and Fig 10, respectively.

Fig9 Delay of Comparator Topologies at 180nm and 90nm Technology

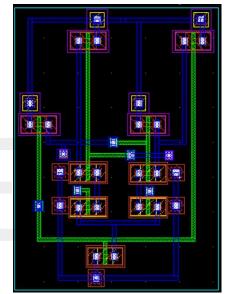

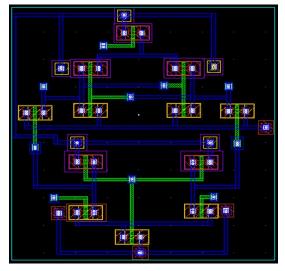

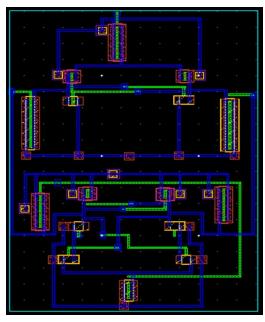

The layout of conventional dynamic comparator is shown in Fig 11 which is  $6.02\mu m^* 8.105\mu m$  and layout of double tail dynamic comparator is shown in Fig 12 i.e.  $8.28\mu m$  \*  $9.13\mu m$  in dimensions whereas the area occupied by proposed compara-

tor is 12.82 $\mu m^*$  18.715 $\mu m$  which is shown in Fig 13 when designed in 90nm technology.

Fig10 Delay of Comparator Topologies at 180nm and 90nm

Fig11 Layout of Conventional Dynamic Comparator

Fig12 Layout of Double Tail Dynamic Comparator

Fig13 Layout of Proposed Comparator

## **6** CONCLUSION

The results were simulated in Cadence Virtuoso Analog Design Environment with GPDK 90nm technology and 180nm technology. The proposed structure shows significantly lower power dissipation, higher speed compared to the dynamic comparators present in the literature. The average power of proposed comparator in 90nm technology is 83.92% reduced than at 180nm technology due to the decrease in channel length of the transistors and it is 62.78% reduced as compared to the double dynamic tail comparator. The delay of proposed comparator is 28% reduced when compared to the double dynamic tail comparator in 90nm technology. Thus, the proposed transistor is energy efficient when compared to other topologies at 90nm and 180nm technologies. The transistor count in the proposed comparator is more to some extent among all the comparators analyzed. From simulation results, we can see that power dissipation is more due to the switching of the transistors because of the high speed operation of the comparator, so the decreasing of dynamic power could be a work for future. The die area could be further reduced. Offset voltage optimization can be another topic of interest.

### REFERENCES

[1] A.-J. Annema, B. Nauta, R. van Langevelde, and H. Tuinhout, "Analog circuits in ultra-deep-submicron CMOS," IEEE Journal of Solid-State Circuits, vol. 40, no. 1, Jan. 2005, pp. 132–143.

[2] H. J. M. Veendrick, "The behavior of flip-flops used as synchronizers and prediction of their failure rate," IEEE Journal of Solid-State Circuits, vol. SSC-15, no. 2, Apr. 1980, pp. 169–176.

[3] K. Uyttenhove and M. S. J. Steyaert, "A 1.8-V 6-Bit 1.3-GHz flash ADC in 0.25-  $\mu m$  CMOS," IEEE Journal of Solid-State Circuits, vol. 38, no. 7, Jul. 2003, pp. 1115–1122.

[4] V. Ferragina, N. Ghittori, and F. Maloberti, "Low-power 6-bit flash ADC for high-speed data converters architectures," Proceedings of IEEE

International Symposium of Circuits Systems, 2006, pp. 3930–3933.

[5] C. Paulus, H.-M. Blüthgen, M. Löw, E. Sicheneder, N. Brüls, A. Courtois, M. Tiebout, and R. Thewes, "A 4 GS/s flash ADC in 0.13  $\mu$ m CMOS," Proceedings of IEEE Symposium of VLSI Circuits, 2004, pp. 420–423.

[6] K.-L. J. Wong and C.-K. K. Yang, "Offset compensation in comparators with minimum input-referred supply noise," IEEE Journal of Solid-State Circuits, vol. 39, no. 5, May 2004, pp. 837–840.

[7] Y. Okaniwa, H. Tamura, M. Kibune, D. Yamazaki, T.-S. Cheung, J. Ogawa, N. Tzartzanis, W. W. Walker, and T. Kuroda, "A 40-Gb/s CMOS clocked comparator with bandwidth modulation technique," IEEE Journal of Solid-State Circuits, vol. 40, no. 8, Aug. 2005, pp. 1680–1687.

[8] S. Mishra, V. Pandel et.al "Design and Operating Characteristics of Voltage Comparator Using MTCMOS Circuits," Proceedings of 7th International Conference on Intelligent Systems and Control (ISCO), Jan. 2013, pp. 256-260.

[9] S. Khurana et.al "Comparative Analysis: Power Reversible Comparator Circuits 90 nm Technology," 7th Asia Modeling Symposium IEEE, 2013, pp. 103-107.

[10] B. Rezaeii, "A 125MS/s Self-latch Low-Power Comparator in  $0.35\mu m$  CMOS Process," 21st Iranian Conference on Electrical Engineering (ICEE), IEEE 2013, May 2013, pp. 1-4.

[11] A. Baradaranrezaie et.al "A 1GS/s Low-Power Low-Kickback Noise Comparator in CMOS Process," 20th European Conference on Circuit Theory and Design (ECCTD), IEEE, Aug. 2011, pp. 106-109.

[12] M. Mohammadi et.al "A 0.5V 200 MHz Offset Trimmable Latch Comparator in Standard 0.18 µm CMOS Process," 21st Iranian Conference on Electrical Engineering (ICEE), IEEE, vol 5, May 2013, pp. 1-4.

[13] M. Akbari, "A New Rail-to-Rail Ultra Low Voltage High Speed Comparator," 21st Iranian Conference on Electrical Engineering (ICEE), IEEE, May 2013, pp. 1-6.

[14] H.Vardhini, S. Palagiri et. al., "Design Development & Performance Analysis of High Speed comparator for Reconfigurable ADC with 180 nm TSMC technology," IEEE 15th International Conference on Advanced Computing Technologies (ICACT), Sept. 2013, pp. 1-6.

[15] P. Gandhil et. al., "High Performance CMOS Voltage Comparator," Nirma University International Conference on Engineering (NUICONE), IEEE, Nov. 2013, pp. 1-5.

[16] K. Kuo, "Capacitive Dynamic Comparator with Low Kickback Noise for Pipeline ADC," IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC), Jun. 2013, pp. 1-2.

[17] U. Soni et.al, "Design of High Speed and leakage Tolerant CMOS Comparator in UDSM Technology," Third International Conference on Advanced Computing & Communication Technologies, IEEE, Apr. 2013, pp. 326-329.

[18] S. Kazeminia, "Improved Single-Stage Kickback-Rejected Comparator for High Speed and Low Noise Flash ADCs," European Conference on Circuit Theory and Design (ECCTD), IEEE, Sept. 2013, pp. 1-4.

[19] H. Srivastaval and J. Jain, "Low Power Latched Comparator Based Second Order Sigma Delta Modulator (SDM)," International Conference on Control, Automation, Robotics and Embedded System (CARE) IEEE, Dec. 2013, pp. 1-6.

[20] P. Bicleanu and A. Salceanu, "Signal Integrity Issues due to ESD events in High-Speed CMOS Comparator," IEEE 8th International Symposium on Advanced Topics in Electrical Engineering, May 2013, pp. 1-6.

[21] S. A. Hafeez and B. Parhami, "Scalable Digital CMOS Comparator Using a Parallel Prefix Tree," IEEE Transactions on VLSI Systems, vol. 21, no. 11, Nov. 2013, pp. 1989-1998.

[22] J. Yang et.al "A High-precision, Low Offset Voltage, Delay Stability

Comparator," Fifth International Conference on Intelligent Human-Machine Systems and Cybernetics, vol. 1, Aug. 2013, pp. 466-469.

[23] A. S. Anand, "High-Performance 64-Bit Binary Comparator," IEEE International Conference on Reliability, Optimization and Information Technology - ICROIT, Feb. 6-8, 2014, pp. 512-519.

[24] F. Moradi et .al, "A leakage- Tolerant CMOS Comparator in ultra deep submicron CMOS Technology," XXII conference on design of circuits and Integrated system, 2007.

[25] A. Roozbehani and O. Hashemipour, "A Modified Structure for High-Speed and Low-Overshoot Comparator-Based Switched-Capacitor Integrator," IEEE 21st Iranian Conference on Electrical Engineering (ICEE), May 2013, pp. 1-5.

[26] V. Milovanovi et.al, "A Fully Differential CMOS Self-Biased Two-Stage Preamplifier-Latch Threshold Detection Comparator," IEEE International Symposium on Circuits and Systems (ISCAS), May 2013, pp. 606-609.

[27] C. T. Chiang et.al, "A CMOS Optical-Comparator-Based Velocity and Direction Motion Sensor," Proceedings of 2013 IEEE International Conference on Mechatronics and Automation, IEEE, 2013, pp 191-195.

[28] P. Chuang, "A 167-ps 2.34-mW Single-Cycle 64-Bit Binary Tree Comparator with Constant-Delay Logic in 65-nm CMOS," IEEE Transactions on Circuits and Systems, vol. 61, no. 1, Jan. 2014, pp. 160-171.

[29]. S. Phaneendra et.al, "An Optimized Design of Reversible Quantum Comparator,"

27th International Conference on VLSI Design and 2014 13th International Conference on Embedded Systems, Jan. 2014, pp. 557 – 562.

[30] C.H. Huang and J.S. Wang, "High-performance and power-efficient CMOS Comparator," IEEE Journals of Solid State Circuit, vol. 38, no. 2, Feb 2003, pp. 254-262.

[31] S. Yewale and R. Gamad, "Design of low power and high speed CMOS comparator for A/D converter Application," Wireless Engineering and Technology, vol. 3, Apr. 2012, pp. 90-95.

[32] S. Mashhadi and R. Lotfi, "Analysis and Design of a Low-Voltage Low-Power Double-Tail Comparator," vol. 22, no. 2, Feb. 2014, pp. 343-352.

[33] K. Yoshioka and A. Shikata, "An 8 bit 0.3–0.8 V 0.2–40 MS/s 2bit/Step SAR ADC With Successively Activated Threshold Configuring Comparators in 40 nm CMOS," IEEE Transactions on VLSI Systems, no. 99, Feb. 2014.

[34] T.H. Kong, G.H. Cho and S.W. Hong, "A 0.791 mm2 On-Chip Self-Aligned Comparator Controller for Boost DC-DC Converter Using Switching Noise Robust Charge-Pump," IEEE Journal of Solid-State Circuits, vol. 49, no. 2, Feb. 2014, pp. 502-512.

[35] D.N. Kapadia and P.P. Gandhi, "Implementation of CMOS Charge Sharing Dynamic Latch Comparator in 130nm and 90nm Technologies," Proceedings of IEEE Conference on Information and Communication Technologies, Apr. 2013, pp. 16-20.

[36] Y.Sun, Y.S. Wang and F.C. Lai, "Low Power High Speed Switched Current Comparator," 14th IEEE International Conference on Mixed Design of Integrated Circuits and Systems, Jun. 2007, pp. 305-308.

## **6 CONCLUSION ABOUT THE AUTHORS**

Anu, completed her B.Tech in Electronics and Communication Engineering from Maharshi Dayanand University, Rohtak in 2012. She has done Master of Technology (M.Tech) in VLSI Design at ITM University, Gurgaon. Her interest includes Digital Design, ASIC Design, VLSI Testing and Verification. R. M. Singh, an Associate Director, Scientist 'G' in ISSA, Defence R&D Organisation, Metcalfe House, Delhi, India. He did his graduation from B.H.U., Varanasi and post graduation from Roorkee University. He is working in DRDO since last 32 years in various disciplines pertaining to Electronics and Communications Engineering. The areas of specialization are communication/ computer networks and embedded systems along with device technology. In addition, he had worked in computing hardware design and implementation upto instruction level.

| Table 5.1 | Comparative | Analysis c          | f Results  |

|-----------|-------------|---------------------|------------|

| 10010-0.1 | Comparative | 7 11 10 1 9 5 1 5 0 | i itosuits |

| S. No.   | Comun        | Hanal   | Davik       |          | Draw       |           |

|----------|--------------|---------|-------------|----------|------------|-----------|

| 5. INO.  | Conventional |         | Double Tail |          | Proposed   |           |

|          | Dynamic      |         | Dynamic     |          | Comparator |           |

|          | Comparator   |         | Comparator  |          |            |           |

| Tech-    | 180nm        | 90nm    | 180nm       | 90nm     | 180nm      | 90nm      |

| nology   |              |         |             |          |            |           |

| Average  | 27.65        | 12.69   | 21.53       | 7.85     | 18.17      | 2.921     |

| Power    | μW           | μW      | μW          | μW       | μW         | μW        |

| Static   | 948nW        | 758nW   | 879nW       | 496nW    | 578nW      | 114nW     |

| Power    |              |         |             |          |            |           |

| Dynam-   | 26.66        | 11.932  | 20.651      | 7.35     | 17.592     | 2.807     |

| ic Pow-  | μW           | μW      | μW          | μW       | μW         | μW        |

| er       |              |         |             |          |            |           |

| Delay    | 3.017ns      | 1.93ns  | 796.75ps    | 361.2ps  | 578.12ps   | 259.7ps   |

| Energy   | 0.276pJ      | 0.0761  | 0.215pJ     | 0.0471pJ | 0.181pJ    | 0.01752pJ |

|          |              | 4pJ     |             |          |            |           |

| Settling | 9.79 ns      | 5.96ns  | 9.67 ns     | 5.988 ns | 9.99 ns    | 5.978 ns  |

| Time     |              |         |             |          |            |           |

| Speed    | 331.4        | 518.13  | 1.256       | 2.76 GHz | 1.73 GHz   | 3.850     |

|          | MHz          | MHz     | GHz         |          |            | GHz       |

| PDP      | 83.420fJ     | 24.49fJ | 17.152fJ    | 2.835fJ  | 10.504fJ   | 0.7585fJ  |

| Area     | 18.46µm      | 6.02µ   | 26.945µm    | 8.28µm * | 25.62µm*   | 12.82µm*  |

|          | *            | m *     | *36.545µ    | 9.13µm   | 40.11µm    | 18.715µm  |

|          | 20.03µm      | 8.105   | m           |          |            |           |

|          |              | μm      |             |          |            |           |